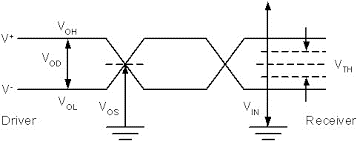

LVDS(低電圧差動信号)は最新のフラット・パネル・ディスプレイにおけるデジタル画像伝送回路の標準仕様です。従来の液晶フラット・パネル・ディスプレイ(FPD)から今日の有機ELフラット・パネル・ディスプレイ(FPD)においても、LVDSの技術仕様は常に革新的です。FPDでの画像伝送は、送信回路で赤、青、緑の3原色の多ビット信号と同期信号をシリアライズして1つのクロック差動信号を含む複数レーンのLVDS信号に変換して送信し、受信回路でそれらをデシリアライズして画像信号や同期信号に復元します。LVDSのレーンの数はディスプレイのサイズなどによって決まります。基本的に、LVDSの電気的特性は非常に単純です。その伝送速度は最大800Mb/sに達することができ、そのクロック速度は最大100MHzに達することができます。伝送される差動信号の振幅は350mVと低電圧なので、伝送効率は非常に高くなります。

LVDS低電圧差動信号伝送アーキテクチャ

現在の業界標準として、オシロスコープと高速差動プローブを使用してLVDS伝送の信号品質を検証しています。テストはデータ信号とクロック信号の測定に分けることができます。LVDSデータ差動信号ペアの伝送速度は最大800Mb/sに達する可能性があります。オシロスコープは5次高調波も観測できることが要求されるので、基本的なテスト要件を満たすために2GHz帯域幅のオシロスコープ、その帯域幅を満足する高速差動プローブが必要となります。さらに、テスト項目には、データ信号のアイ・ダイアグラム・テスト、およびクロック信号の立ち上がりエッジ時間テストが含まれます。LVDS信号テストの標準規格がないので各システム設計メーカーには独自のテスト仕様がありますが、上記の2つのテスト仕様は最も基本的であり、重要なものです。アイ・ダイアグラム・テスト・アーキテクチャに関しては、オシロスコープでデータ差動信号ペアを差動プローブで観測し、アイ・ダイアグラム・テスト機能をオンにします。アイ・ダイアグラムのサイズを調整し、アイ・ダイアグラムの高さ、幅、クロスポイントのパーセンテージ、立ち上がり時間、立ち下がり時間、Qファクタなどを観察します。クロック差動信号については、立ち上がりエッジの信号状態を観察する必要があります。プリシュートやリップルなどの項目も重要です。

LVDS アイ・ダイアグラム・アーキテクチャ

以下は、自動車用オーディオ装置のディスプレイのLVDS信号テストの例です。

リゴル PVA7250 高速差動プローブの接続

リゴル MSO8204 オシロスコープによるアイ・ダイアグラム・テスト

以上、リゴル MSO8204 オシロスコープによるアイ・ダイアグラム・テストでした。

お問い合わせ

お問い合わせ

〒170-0005 東京都豊島区南大塚3-45-5 5階

シェア